# **Comparison between Conventional Ripple Carry Adder and Reversible Ripple Carry Adder Using Peres Gate and HNG Gate**

K Arunamanjusha, T Kalyani, S Sowjanya, S Sravankumar, A Shruthi, R Dileep Department of ECE, MLR Institute of Technology, Hyderabad, India Corresponding Author: K Arunamanjusha

-----ABSTRACT------Reversible logic plays an important role in quantum computing to synthesis in electric circuits. In modern systems, power dissipation is high due to continuous switching of inbuilt components. In present generations, the difficulty of chips is increasing as more number of components or devices is fabricated on a single chip. Due to high density of disk, the power consumption is high. To reduce power consumption alternate method is power optimization method. The important method to achieve the optimization in power is by using reversible logic. It can be developed by low power CMOS technology, the reversible logic can be proposed for reducing quantum

cost. It produces garbage outputs. In this paper we are implementing the 16 bit reversible ripple carry adder using Peres and HNG gate .

KEYWORDS: quantum computing, Peres gate, garbage outputs, adder design, reversible logic.

\_\_\_\_\_ Date of Submission: 21-05-2018

Date of acceptance: 05-06-2018

#### Ι **INTRODUCTION**

\_\_\_\_\_

In this process thereversible computation can be done to some extent. It uses deterministic transitions from one state to another state. An obligatory condition for reversibility is the relation between the inputs and outputs of non-zero probability to their substitute inputs must be similar to their outputs. It is in the form of unconventional computing [1-2]. The most closely related types of reversible computing is based on the physical performance of the device and the logical performance of the device.

1.1 **Physical reversibility**: A process is said to be physically reversible if there is no increase in physical property. In a non deterministic process the relation depends on past and present states is not a single valued function. Thisimplementation controls and characterizes the physical dynamics of mechanisms to carry out the arithmetic operations. Each logical operationaccumulate anirrelevantamount of mechanism in its physical state, else the arithmetic operations can be carried out by active energy and the majority energy is retained and reused for any physical operations [3]. In present days, a wide variety of reversible device concepts, logic gates, electronic circuits, processor architectures, have been designed and analysed .

1.2 Logical reversibility: Before implementation one should identify its limits and the cost that can assigned in gate levelcircuits. In this reversible logic, the NOT gate is irreversible because it can be done in conventional logic [4]. The XOR gate is irreversible because its two inputs cannot be uniquely reconstructed from its single output. However, a reversible version of the XOR gate the CNOT controlled NOT-can be defined by preserving one of the inputs. The three-input variant of the CNOT gate is called the toffoli gate consider a, b as two inputs and c would be the third input. (c is XORed with (a&b)) with c=0. Which gives AND function, i.e., a.b=1. Thus, the Toffoli gate is universal and can implement any reversible and can be implemented by any Boolean function [4].(Given enough zero-initialized ancillary bits). More generally, reversible gates that consume their input have no more inputs than outputs. A reversible circuit connects reversible gates without fan outs and feedbacks. Therefore, each circuit contains an equal number of input and output wires. It has been observed that for every bit of information loss in logic computation that are not reversible. A gate is considered as a reversible only if for each defined input there is a defined output [5]. A reversible logic is having same number of inputs and same no, of outputs. This circuits can perceive only balanced functions and unbalanced functions can be considered as garbage outputs .

### 1.3 Advantages:

- It uses a minimum number of garbage outputs.

- It uses a minimum number of reversible gates.

- It uses a minimum constant inputs.

# II LITERATURE SURVEY:

It is not possible to realize quantum computing without implementation of reversible logic. To implement a reversible logic function one should know the basic and important definitions .

Garbage outputs: garbage output is defined as an unwanted output data without affecting its input data

**Reversible function:** Boolean functions are irreversible  $F(x_1, x_2...x_n)$  only when number of inputs and outputs are equal. And any output pattern has a unique one to one mapping between inputs and outputs .

Gate count: The gate count is major cost metric in the evaluation of reversible circuit .

Delay: he delay of the circuit depends on the number of gates involved in the operation .

**Quantum cost: the total number of gates** which realizes the given function is also known as quantum cost. It varies depend on number of inputs and outputs of gates .

#### 2.1 Some of the basic reversible logic gates :

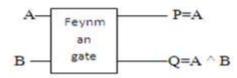

(a). Feynman gate: The basic 2\*2 Feynman logic gate is shown in the below fig 1. It is having 2 inputs (A, B) and 2 outputs (P=A, Q=A^B). The working function is shown in the below Table 1

Fig 1: Feynman gate

| A | В | P=A | Q <b>=</b> A^B |

|---|---|-----|----------------|

| 0 | 0 | 0   | 0              |

| 0 | 1 | 0   | 1              |

| 1 | 0 | 1   | 1              |

| 1 | 1 | 1   | 0              |

# Table1: Truth table of Feynman gate

(b). Fred kin gate: Is a 3 bit gate that swaps the last two bits if the first bit is 1, i.e., a controlled swap operation. It is having 3 inputs(A, B, C) and 3 outputs (P=A, Q=A'B  $\land$  AC, R=AB  $\land$  A'C. to understand the working of fredkin gate refer the truth table as shownin Table 2. The basic structure can be shown fig 2

| A —                 |         | <b>−−− ₽</b> =A |  |  |  |

|---------------------|---------|-----------------|--|--|--|

| в—                  | FREDKIN | Q= A'B ^ AC     |  |  |  |

| С—                  | GATE    | $R = AB^AC$     |  |  |  |

| Fig 2: Fredkin gate |         |                 |  |  |  |

| Α | В | С | P=A | Q <b>=</b> A'B | R=AB |

|---|---|---|-----|----------------|------|

|   |   |   |     | ^AC            | ^A'C |

| 0 | 0 | 0 | 0   | 0              | 0    |

| 0 | 0 | 1 | 0   | 0              | 1    |

| 0 | 1 | 0 | 0   | 1              | 0    |

| 0 | 1 | 1 | 0   | 1              | 1    |

| 1 | 0 | 0 | 1   | 0              | 0    |

| 1 | 0 | 1 | 1   | 1              | 0    |

| 1 | 1 | 0 | 1   | 0              | 0    |

| 1 | 1 | 1 | 1   | 1              | 1    |

**Table 2: Truth Table**

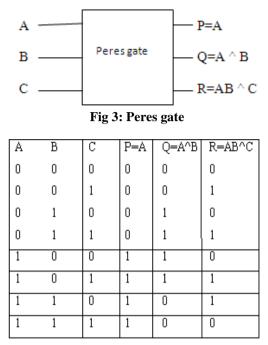

(c). Peres gate: it is a 3\*3 gate which is having three inputs (A, B, C) and three outputs (P=A, Q= A^B, R= AB ^ C shown in fig (3). Working can be explained in truth table .

# Table3: truth table for Peres gate

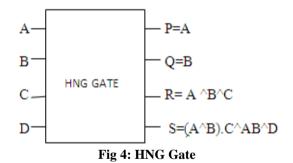

(d). HNG gate: it is a 4\*4 reversible gate. It is having 4 inputs(A,B,C,D) and 4 outputs (P=A, Q=B, R= A  $^BC$ , S=(A^B).C^AB^D is shown in fig (4) and working can be explained by truth table in table 4.

| A | в | С | D | P=A | Q <b>=</b> B | R=A^B^C | S=(A^B) |

|---|---|---|---|-----|--------------|---------|---------|

|   |   |   |   |     |              |         | .C^AB^D |

| 0 | 0 | 0 | 0 | 0   | 0            |         | 0       |

| 0 | 0 | 0 | 1 | 0   | 0            | 0       | 1       |

| 0 | 0 | 1 | 0 | 0   | 0            | 1       | 0       |

| 0 | 0 | 1 | 1 | 0   | 0            | 1       | 1       |

| 0 | 1 | 0 | 0 | 0   | 1            | 1 [     | 0       |

| 0 | 1 | 0 | 1 | 0   | 1            | 1       | 1       |

| 0 | 1 | 1 | 0 | 0   | 1            | 1       | 1       |

| 0 | 1 | 1 | 1 | 0   | 1            | 1       | 0       |

| 1 | 0 | 0 | 0 | 1   | 0            | 1       | 0       |

| 1 | 0 | 0 | 1 | 1   | 0            | 1       | 1       |

| 1 | 0 | 1 | 0 | 1   | 0            | 1       | 1       |

| 1 | 0 | 1 | 1 | 1   | 0            | 1       | 0       |

| 1 | 1 | 0 | 0 | 1   | 1            | 0       | 1       |

| 1 | 1 | 0 | 1 | 1   | 1            | 0       | 0       |

| 1 | 1 | 1 | 0 | 1   | 1            | 0       | 1       |

| 1 | 1 | 1 | 1 | 1   | 1            | 0       | 0       |

Table 4: Truth Table for HNG gate

# III PROPOSED METHOD:

In the proposed method we design and compared the reversible ripple carry adder with conventional ripple carry adder. We are using different reversible gates to design ripple carry adder using Peres gateand HNG gate .

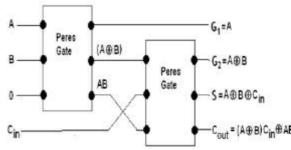

# Peres gate:

Fig 5: 1 bit Peres gate

Full adder is a circuit which is used to perform arithmetic operations the output equations can be written as  $Sum=A \bigoplus B \bigoplus Cin$

Cout=  $(A \oplus B)$  Cin $\oplus AB$ G1= A G2= A $\oplus B$

Using two 3\*3 Peres gates the output of the reversible logic circuit consists of two garbage values and one constant input with an efficient quantum cost is shown in fig 5.

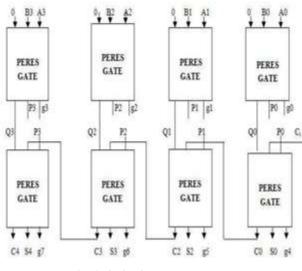

**Design of 16 bit ripple carry adder using Peresgate**: The full adder is a block of ripple carry adder which includes binary full adder .In the ripple carry adder circuit for the first full adder block we are giving three inputs (A0, B0, Cin), the third input Cin=0. The block diagram of four bit ripple carry adder using Peres gate is shown below. For implementing a 16 bit reversible ripple carry adder is 8.Therefore to construct a 16 bit ripple carry adder 32 Peres gates are required [7].

Comparison between conventional ripple carry adder and reversible ripple carry adder using Peres

Fig 6: 4 bit ripple carry adder

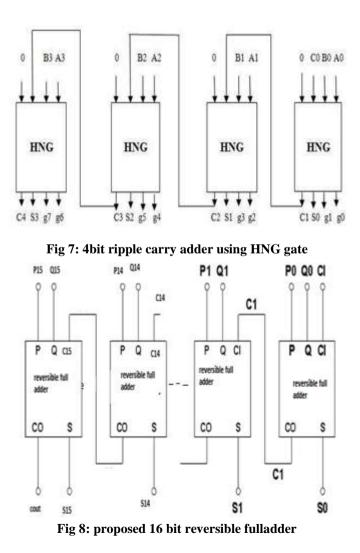

The block diagram of four bit ripple carry adder using HNG is shown in Fig for constructing a four bit reversible ripple carry adder using HNG, 4 HNG are essential. Hence the total gate count for four bit Ripple carry adder is 4. Therefore to construct a 16 bit ripple carry adder 16 HNG are Needed[8].

# IV RESULTS AND DISCUSSIONS:

The proposed Peres ripple carry adder is implemented and resulted by using Verilog and simulated in Xilinx 9.2 I.The output waveform for 16 bit and 4 bit reversible ripple carry adders is shown in below fig 8.

| Current Simulation |       | 0         | 200                                    | 400                                     | j600               | 800               |

|--------------------|-------|-----------|----------------------------------------|-----------------------------------------|--------------------|-------------------|

| Time: 1000 ns      |       |           |                                        |                                         |                    |                   |

| Sum[7:0]           | 8100  |           |                                        |                                         |                    |                   |

| o Cout             | χ     |           |                                        |                                         | 1                  |                   |

| A(7:0)             | 81107 | 00000000  | 00000000000                            | 000000000000000000000000000000000000000 | 26066000000000     | TREES CONTRACTOR  |

| <b>B</b> [7:0]     | 81106 | COCCOCO ( | XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX | XXXXXXXXXXXXXXXXX                       | ARRONAL CONTRACTOR | NERVECER DI CARDO |

| o Cin              | 0     |           |                                        |                                         |                    |                   |

|                    |       |           |                                        |                                         |                    |                   |

|                    |       |           |                                        |                                         |                    |                   |

# Fig 9:Simulation results for 4 bit ripple carry adder

| B 81 Sum(15.0)         1         C(////////////////////////////////////                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| • \$1 4150 1. (D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C.)(D.C. |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Q. Cin 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

### Fig 10:Simulation output for 16 bit ripple carry adder

The comparison of two reversible Ripple Carry Adder based on three parameters i.e. Gate count, Garbage output and Quantum cost is shown in the table

| Parameters     | 16 bit reversible adder using Peres gate | 16 bit reversible adder using HNG gate |

|----------------|------------------------------------------|----------------------------------------|

| Gate count     | 32                                       | 16                                     |

| Garbage output | 32                                       | 32                                     |

| Quantum cost   | 128                                      | 96                                     |

| Quantum cost   |                                          |                                        |

### Table 5:Comparison between Reversible Ripple Carry Adders

### CONCLUSION

v

This paper presents the design and simulation of 16 bit reversible ripple carry adder using Peres gate and HNG gate. The power delay is calculated for 16 bit reversible ripple carry adder. Also, the time delay between conventional ripple carry adder and reversible ripple carry adder using Peres gate and HNG gate was found, 8.16ns, 7.79ns, and 7.76ns

### **REFERENCES:**

- [1]. Landauer, R., "Irreversibility and heat generation in the computing process", IBM J. Research and Development, 5(3): pp. 183-191, 1961

- [2]. Thapliyal H, M. B.Shrinivas." A New Reversible TSG Gate and Its Application for Designing Efficient Adder Circuits". Centre for VLSI and Embedded System Technologies International Institute of Information Technology, Hyderabad, 500019, India

- [3]. 3.Siva Kumar Sastry, HariShyam Shroff, Sk.NoorMahammad, V. Kamakoti" Efficient Building Blocks for Reversible Sequential Circuit Design" 1-4244-0173- 9/06/\$20.00©2006IEEE

- [4]. Thapliyal H, Ranganathan N.," Design of Reversible Latches Optimized for Quantum Cost, Delay and Garbage Outputs" Centre for VLSI and Embedded System Technologies International Institute of Information Technology, Hyderabad, 500019, India.

- [5]. H.r.bhagyalakshmi, M.k.venkatesha," an improved design of a multiplier using reversible Logic gates" International Journal of Engineering Science and Technology Vol. 2(8), 2010, 3838-3845

- [6]. B.Raghukanth, B.Murali Krishna, M. Sridhar, V.G. SanthiSwaroop —A DISTINGUISH BETWEEN REVERSIBLE AND CONVENTIONAL LOGIC GATES I, International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 2, Issue 2,Mar-Apr 2012, pp.148-151

- [7]. Rashmi S, Praveen, and Tilak G, —Design of Optimized Reversible BCD Adder/Subtract or, IACSIT International Journal of Engineering and Technology, Vol.3, No.3, June 2011.

# Comparison between conventional ripple carry adder and reversible ripple carry adder using Peres

[8]. Sudharshan M, H R Bhagyalakshmi, M K Venkatesha, — Novel Design of one digit high speed Carry select BCD Subtractor using Reversible logic gatesl, International Journal of Emerging Technology and Advanced Engineering (ISSN 2250-2459, Volume 2, Issue 7, July 2012)

K Arunamanjusha." Comparison between Conventional Ripple Carry Adder and Reversible Ripple Carry Adder Using Peres Gate and HNG Gate." The International Journal of Engineering and Science (IJES) 7.5 (2018): 59-65