# Weka Hertz Clock Based Weka Bits Per Second P.R.B.S Data Array Encryption A.S.I.C For Parallel Pipelined V.L.I.W Array Based Big Data Distributed Processing /Cloud/Internet Grid Computing Wireless Applications & Products

Prof. P.N.V.M Sastry<sup>1</sup>, Dr.D.N.Rao<sup>2</sup>, Dr.S.Vathsal<sup>3</sup>

<sup>1</sup>Dean- IT EDA Software Industry CELL, R&D CELL & ECE, J.B.R.E.C., Moinabad, Hyderabad-75, India <sup>2</sup> Former Principal-J.B.I.E.T & Dean -R&D, J.B.I.E.T, Moinabad, Hyderabad-75, India <sup>3</sup> Professor, I.A.R.E, Hyderabad, India

### ------ABSTRACT------

The Aim is to Implementation of Weka Hertz Clock P.R.B.S Data Frame Array Encryption Soft H.D.L A.S.I.C I.P Core Architecture Design using Serial to Parallel Data Array Encoder for Parallel Distributed Array Data Computing System based Ultra High Speed Wireless System Software Applications and Products — A.S.I.C Data Serializer-De-Serializer, cloud, cluster, grid, WI-FI,GI-FI Internet computing, 3G,4G,5G Wireless System Software Products and Applications. This Design Architecture contains P.R.B.S Data Frame Registers of 32/64 bit Length, 8 Serial to Parallel Data Encoder Arrays and Weka Clock Frequency Baud Rate Generator /Oscillator and Coding Done by V.H.D.L and Verilog H.D.L Software. Design Implementation Done by Xilinx ISE 9.2i Software I.D.E and Altera Quartus II MODELSIM Simulation Tool. Programming and Debugging Done by Xilinx F.P.G.A Development Kit Xilinx XC 3S 200 TQ 144 F.P.G.A Chip. Design Implementation done through SPARTAN III F.P.G.A.

**Keywords:** PRBS – Pseudo Random Binary Sequence, F.P.G.A – Field Programmable Gate Array, A.S.I.C-Application Specific Integrated Circuit. V.H.D.L – Very High Speed Integrated Circuit Hardware Description Language, I.S.E- Integrated Software Environment. I.D.E- Integrated Development Environment

Date of Submission: 17 May 2016 Date of Accepted: 22 August 2016

#### I. INTRODUCTION

In Hi-tech Smart Computing Real Time Digital Industrial World & Hi-tech Real time Software Computing World, Every item is smart computing w.r.t speed, power, potential, frequency, Size, performance, Reliability according to Electronic Design and Software Quality Standards. So I've Designed Weka PRBS Data Frame Array Encryption Soft H.D.L A.S.I.C S.O.C I.P Core, using Serial to Parallel Array Encoder. Here I am Implementing Different Patterned Sequences like 2e<sup>7</sup>-1, 2e<sup>10</sup>-1, 2e<sup>15</sup>-1, 2e<sup>23</sup>-1, 2e<sup>31</sup>-1, 2e<sup>48</sup>-1, 2e<sup>63</sup>-1 for High Speed Data Encryption of identification of property of Different PRBS Seed Word Patterns according to Tapping Frequency Standards as per C.C.I.T.T- I.T.U O.150/O.151/O.152 etc. Simply it is one of the Parallel Processing Technique for Randomization of Data from Plain text format to Cipher Text Seed word format. More suitable application are 3G,4G,5G Wireless Mobile and Multimedia ,Consumer Electronic Automation, Medical Diagnostic ,Image & Video Array Processing, Cryptography Automation, Smart Robot Automation, Industrial Automation, Avionics, Automotive Smart WiFi, Internet, Cloud, Cluster, Grid Computing, Super VLIW Parallel Array Distributed Pipe Lined Computing Arrays and Advanced Graphics and Network On Chip Array Cards for MODEMS, Routers. Here the Speed of Weka P.R.B.S Data Frame Array Encryption is in terms of Weka bits per second (Wbps) for all above P.R.B.S Pattern Sequences of different tapping points 7,10,15,23,31 ,48,63 as per Single Data Precision and Double Data Precisions for Big Data Encryption Computing. New Products are all smart Computing Portable Hand Held Digital Automation Applications. This is an Universal IP Core Encrypted Large Automation Data.

Basically The Architecture Contains P.R.B.S – L.F.S.R Data Generator , Weka Clock Frequency Generator, 8 bit Data Encoder Array of different P.R.B.S Data Patten Sequences -2e<sup>7</sup>-1, 2e<sup>10</sup>-1, 2e<sup>15</sup>-1, 2e<sup>23</sup>-1, 2e<sup>31</sup>-1, 2e<sup>48</sup>-1, 2e<sup>63</sup>-1, etc. P.R.B.S Contains Linear Feedback Shift Register of Different Feedback Tapping points 7,10,15,23,31,48,63 etc. Weka Clock Frequency Generator provide Speed 2<sup>100</sup> Clock Cycles per second. Simply 2<sup>50</sup> Clock cycles for Active High Clock Pulse and 2<sup>50</sup> Clock Cycles for Active low Clock Pulse for processing speed Data Frame Encryption. Estimation Size Of Geometry of P.R.B.S Data Encryption ASIC is In terms of Micro, Nano, and Femto Meters width and Length. The product is mainly suit for Advanced Computing Processors Super V.L.I.W Pipe Lined Distributed Array / Graphics Data Computing Array.

Data Frames Encryption in terms of group of Data Bytes either 4 or 8 Data Bytes width. All the Seed word patterns are processing at an speed of Weka Hertz Clock Frequency Rate outstanding. Speed in terms of Weka Bits per second. This Data Encryption A.S.I.C IP Core suit for all Bus Based Nano /Femto Chip Card Interface Industrial Hardware Card Products / Applications. The Main advantages are more time save and power, reduction of time delays by parallel data encryption technique and high compact and more reliable innovative electronic product. Processing Data is in the form of eye diagrams array. This encryption reduces more bit error rate and A.W.G.N etc.

This Encryption Core Suit Highly Reliable Portable Hand Held Instruments/ Computing products like Mobile Phones, phones, Tablets, Note Book Computers, and eepads. Pen Computers, HiFi Memory Drivers. Large Software Data Compositing Servers, Stations etc. and also Very Suit for Micro/Nano/Femto Boards and Electronic Cards, Graphics Processor Array Cards.

This saves more time and chip complexity, and also more improvement of processing speed of data in terms baud rate Weka Bits per Second for large data computation applications and products like wireless and telecom, data bus communication, Smart consumer electronics, avionics, automotive, image and video, graphics processing, portable multimedia products and applications. This codec is interface with Weka Bytes Memory Shell /SOC for storing large complex data.

# II. WEKA HERTZ P.R.B.S DATA FRAME ENCRYPTION A.S.I.C ARCHITECTURE

# A. Weka Hertz P.R.B.S Data Frame Array Encryption Soft H.D.L A.S.I.C I.P Core Design Architecture

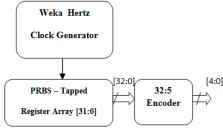

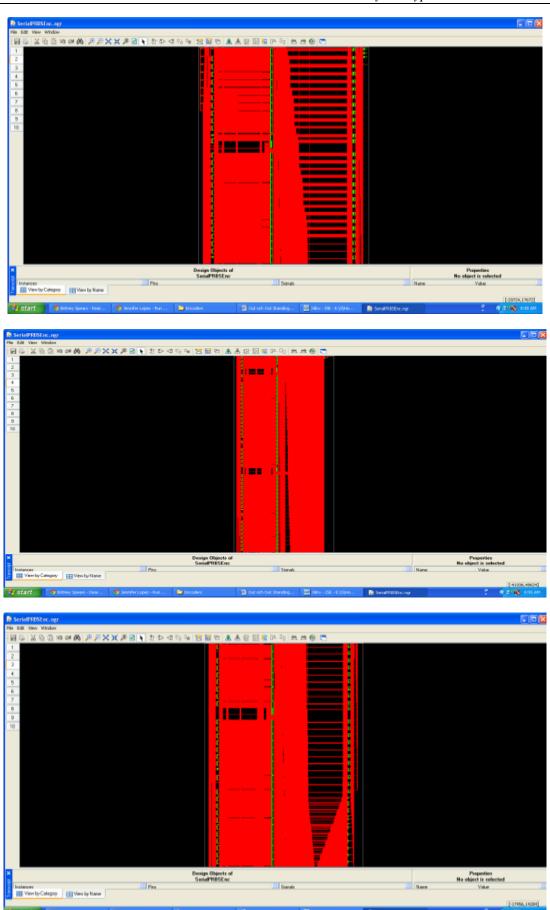

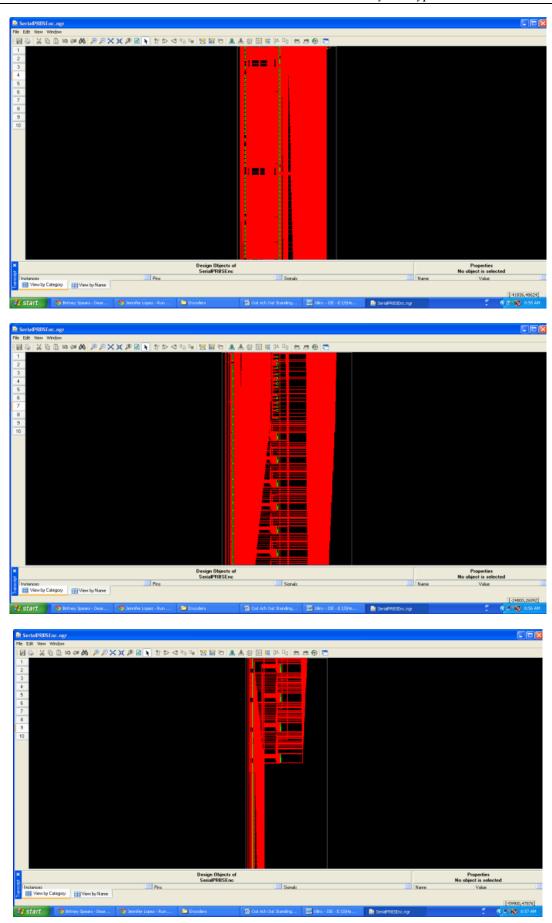

Figure 1.P.R.B.S Tapped Data Frame Array Encryption H.D.L A.S.I.C Architecture

**Description:** This A.S.I.C I.P Core Consists Weka Hertz Clock Generator, P.R.B.S Tapped Register Arrays of Bit Length 32 Bit Data of Different Tapping Points 7,10,15,23,31,48,63 etc. for Identification and Encryption of Pseudo Random Binary Sequences – 2e<sup>7</sup>-1, 2e<sup>10</sup>-1,2e<sup>15</sup>-1,2e<sup>23</sup>-1,2e<sup>31</sup>-1,2e<sup>48</sup>-1,2e<sup>63</sup>-1 etc. and 32:5 Priority Encoder for Encryption of PRBS Data Array Sequences of Different Tapping Pattern Sequences as per ITU CCITT Standards.

### B. P.R.B.S DATA ARRAY ENCRYPTION DETAILED ARCHITECTURE

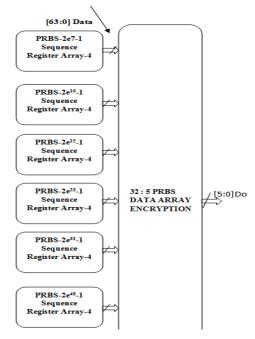

Figure 2. Weka P.R.B.S Data Frame Detailed Architecture

**Description:** This Design Architecture Seven Different Pattern Registers of Different Tapping Elements -7,10,15,23,31,48,63. and This Weka Hertz P.R.B.S Array Consists of Four 7<sup>th</sup> Tapped P.R.B.S Data Registers ,Four 10<sup>th</sup> Tapped P.R.B.S Data Encryption Registers , Four 23<sup>rd</sup> Tapped P.R.B.S Data Encryption Register, Four 31<sup>st</sup> P.R.B.S Data Encryption Register, **all encoded by 32:5 priority Data** Encoder for Identification P.R.B.S Data Frames w.r.t Different Tapping Elements.

# III. WEKA P.R.B.S DATA ENCRYPTION DESIGN FLOW REPORTS

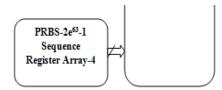

A. R.T.L Design Architecture

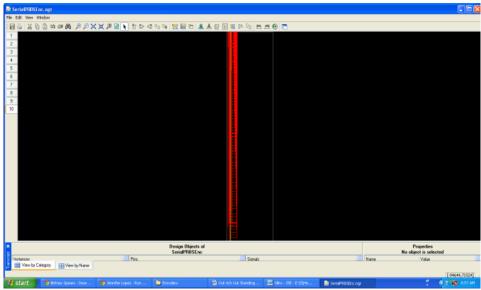

Figure 3. Weka P.R.B.S Data Encryption R.T.L Block

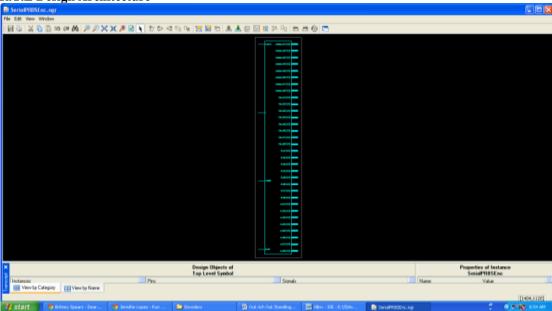

B. R.T.L Design Schematic

www.theijes.com The IJES Page 31

Figure 4. Weka P.R.B.S R.T.L Schematic Design Architecture

# IV. SIMULATION WAVE FORM RESULTS

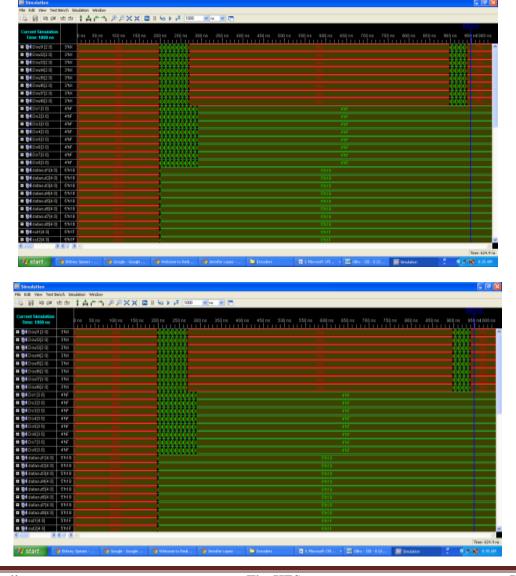

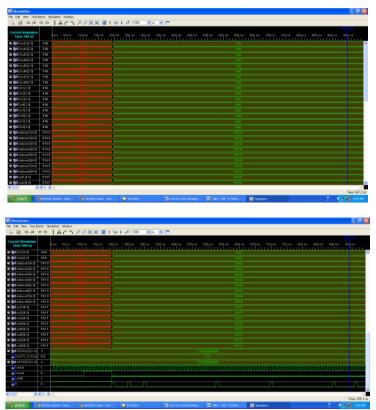

A. Weka Hertz Clock Based P.R.B.S Data Array Encryption A.S.I.C

Figure 6. Weka P.R.B.S Simulation Results

# V. H.D.L SYNTHESIS REPORTS

| HDL SYNTHESIS REPORT     |        |

|--------------------------|--------|

| MACRO STATISTICS         |        |

| # ADDERS/SUBTRACTORS     | : 1    |

| 100-BIT ADDER            | : 1    |

| # COUNTERS               | : 1    |

| 100-BIT UP COUNTER       | : 1    |

| # REGISTERS              | : 65   |

| 1-BIT REGISTER           | : 1    |

| 16-BIT REGISTER          | : 9    |

| 24-BIT REGISTER          | : 8    |

| 3-BIT REGISTER           | : 8    |

| 32-BIT REGISTER          | : 7    |

| 4-BIT REGISTER           | : 8    |

| 5-BIT REGISTER           | : 16   |

| 8-BIT REGISTER           | : 8    |

| # XORS                   | : 32   |

| 1-BIT XOR2               | : 15   |

| 1-BIT XOR3               | : 17   |

| ADVANCED HDL SYNTHESIS I | REPORT |

| MACRO STATISTICS         |        |

| # ADDERS/SUBTRACTORS     | : 1    |

| 100-BIT ADDER            | : 1    |

| # COUNTERS               | : 1    |

| 100-BIT UP COUNTER       | : 1    |

| # REGISTERS              | : 740  |

| FLIP-FLOPS               | : 740  |

| # XORS                   | : 31   |

| 1-BIT XOR2               | : 15   |

| 1-BIT XOR3               | : 16   |

|                          |        |

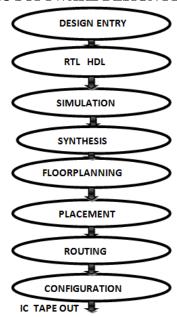

### VI. VLSI – IC SOFTWARE DESIGN FLOW CHART

Figure 7. VLSI IC- EDA Software Design Flow Chart

# VII. CONCLUSION

Designed **Weka PRBS** for Ultra High Speed Wireless Communications, This Design is mainly intended for Ultra Very High Long Distance Communication at the frequency rate of Weka Bits per Second. And this product is very suited for All Very Advanced Smart Digital Computing Communication Products like Advanced 3G,4G,5G,6G, Hi-Fi Space Communication ,Satellite Communication Products. DESIGNED WEKA PRBS DATA ENCRYPTION ASIC IP CORE FOR HIGH SPEED PARALLEL VLIW -DATA COMPUTING / CLOUD COMPUTING/CLUSTER COMPUTING PRODUCTS

#### **ACKNOWLEDGEMENTS**

I would like to Acknowledge to Co-Authors for Valuable Support of Designing the product.

# **REFERENCES**

- [1]. Wikipedia, http://en.wikipedia.org/wiki/ Pseudorandom\_binary\_sequence

- [2]. "ITU-T Recommendations O151, O152 and O153," Tech. Rep.

- [3]. https://www.verigy.com/help/topic/com.verigy.itee.help.smartest.ui.7.1.0/95305.htm

- [4]. SY Hwang, GY Park, DH Kim, KS Jhang, "Efficient Implementation of a Pseudorandom Sequence Generator for High-Speed Data Communications", ETRI Journal, Volume 32, Number 2, April 2010.

- [5]. Xilinx Data Sheet XAPP884 (v1.0) January 10, 2011

- [6]. Ahmad A. and Elabdalla A. M., "An efficient method to determine linear feedback connections in shift registers that generate maximal length pseudo-random up and down binary sequences," *Computer & Electrical Engineering An Int'l Journal (USA)*, vol. 23, no. 1, pp. 33-39, 1997 [7] Ahmad, A., Al Musharafi, M.J.,

- $[7]. \qquad http://en.wikipedia.org/wiki/\ Linear\_feedback\_shift\_register$

### Bibliography - Author Profile

shastrypnvm@gmail.com

Prof P.N.V.M Sastry Currently working with a Capacity of Dean- IT EDA Software - R&D CELL & ECE

DEPARTMENT, He Did Master Degree In Science- M.S Electronics, Under Department Of Sciences, College Of Science & Technology AU -1998.Did PG Diploma In VLSI Design From V3 Logic Pvt Ltd B'Lore-2001, Did M.Tech (ECE) From IASE Deemed University-2005. Currently Pursuing (PhD)-ECE(VLSI), JNTU Hyderabad -2012, Over Past 16 years of Rich Professional Experience with Reputed IT Software Industrial MNC's, Corporate – CYIENT (INFOTECH) (World top CMMi Maturity Level 5 Version 1.2 Confirmed Very few listed Global IT Software Engineering Services MNC), ISiTECH as a world top keen IT

Industrial Software Specialist – World Top Software Engineering Team Leader(Level 6) Eng-Eng-HCM Electronics Vertical & Program Manager – MFG I/C,EDS,BT,NON BT Embedded Software ,Avionics & Automotive Hi-tech Software Engineering Verticals & Departments , Program Lead – Embedded & VLSI & Engineering Delivery Manager – IT Semiconductor Software Engineering Vertical ,at ISiTECH ,

also worked with **Govt R&D, Industrial Organizations, Academic Institutions** of Comparative Designations & Rolls . His Areas Of Interest are VLSI –VHDL, Verilog HDL, ASIC, FPGA & Embedded Software Product Architectures Design & Coding Development .He mentored & Architecting Various Real Time, R&D, Industrial Projects/Products related to VLSI & Embedded System Software & Hardware.. His Key Achievements are Participated Various Top Class International IT MNC Delegates Board Meetings, IT Software MNC Board Meetings(Tier1/2 Level MRM-VP,COO Level), Guided R&D, Industrial, Academic Projects /Products –VLSI-ASIC,FPGA & Embedded & Embedded,VLSI Software Project &/ Program Management & Also Coordinated Various In House & External IT Project Workshops & Trainings At **CYIENT( INFOTECH)** as a I/C- MFG Eng Software Vertical, Also Participated Various National R&D Workshops, FESTS, FDP's &Seminars. Recently He Published Various national & International Journals, Conferences.

# principal\_jbr@yahoo.com

Dr. D.N Rao B.Tech, M.E, Ph.D, principal of JBREC, Hyderabad. His carrier spans nearly three decades in the

field of teaching, administration, R&D, and other diversified in-depth experience in academics and administration. He has actively involved in organizing various conferences and workshops. He has published over 11 international journal papers out of his research work. He presented more than 15 research papers at various national and international conferences. He is Currently approved reviewer of IASTED International journals and conferences from the year 2006. He is also guiding the projects of PG/Ph.D students of various universities

Dr. Vathsal Currently working as a Professor- Aero Dept. I.A.R.E, earlier He Was Dean R&D ,JBIET , He

Obtained PhD from I.I.S.C,Bangalore,also Did Post Doctoral Research in DFVLR,Germany and NASA Goddard Space Flight Centre,USA,and also he worked with keen Designations Scientist E,F,G from Reputed Govt R&D Industry Organizations over past years and closely worked with Dr.A.P.J Abdul Kalam He Published lot of various national, international journals & conferences, He guiding 5 PhD Students from Various universities. He Got Prestigious awarded as a Noble Son of India