## Ultra High Multi Clock Frequency Spectrum -Zetta,Yotta,Xona, Weka Hertz Real Time Clock P.R.B.S Data Framer Array A.S.I.C I.P Core Encryption And Decryption Of Different Patterns For Large/ Big Wireless Data /Cloud/Cluster /Parallel Distributed Computing Stations

Prof P.N.V.M Sastry<sup>1</sup>, Prof.Dr.D.N.Rao<sup>2</sup>, Prof Dr.S.Vathsal<sup>3</sup>

<sup>1</sup>Dean- IT EDA Software Industry CELL, R&D CELL & ECE, J.B.R.E.C, Moinabad, Hyderabad-75, India <sup>2</sup>Former Principal J.B.R.E.C & Dean R&D, J.B.I.E.T, Yenkapally, Moinabad, Hyderabad-75, India <sup>3</sup>Professor, AERO, I.A.R.E, Yenkapally, Hyderabad-75, India

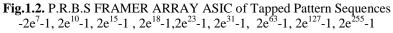

The Aim is to Design and Implement the Ultra High Speed Multi Clock Frequency Spectrum – Tera, Peta, Exa, Zetta, Yotta, Xona, and Weka Hertz Clock P.R.B.S Data Framer Encryption and Decryption Array A.S.I.C S.O.C I.P Core of Different Tapped Seed Word Pattern Sequences -  $2e^{7-1}$ ,  $2e^{10-1}$ ,  $2e^{15-1}$ ,  $2e^{31-1}$ ,  $2e^{48-1}$ ,  $2e^{52-1}$ ,  $2e^{63-1}$ ,  $2e^{127-1}$ ,  $2e^{255-1}$  etc for Large /Big Wireless Data /Cloud/Cluster/Parallel Distributed Computing Stations of Different Data Bytes Storage Capacity – Mega, Giga, Tera, Peta, Exa, Zetta, Yotta, Xona, Weka, Vendica Bits/Bytes Per Second and Data Length in terms of Frames, SuperFrames, Very long word, Super Very Long Word, large array randomized data packets and words for parallel Distributed Computing Data Processing and Storage, execution o f Internet data packets, Cloud /Cluster Data Computing Stations. Implementation Done By soft HDL Procedures – Verilog H.D.L and V.H.D.L & Debugging Done By F.P.G.A –Xilinx 3s4000lfg900-4.

**Keywords:** A.S.I.C- Application Specific Integrated Circuit, S.O.C- System On Chip, IP – Intellectual Property Core, F.P.G.A – Field Programmable Gate Array, P.R.B.S- Pseudo Random Binary Sequence, L.F.S.R-Linear Feedback Shift Register, V.H.D.L –Very High Speed Integrated Circuit Hardware Description Language, C.C.I.T.T-(I.T.U)-Consulting Committee for International Telegraph and Telephone, I.T.U – International Telecom Union.

| Date of Submission: 17 May 2016 | Date of Accepted: 22 August 2016 |

|---------------------------------|----------------------------------|

|                                 |                                  |

#### I. INTRODUCTION

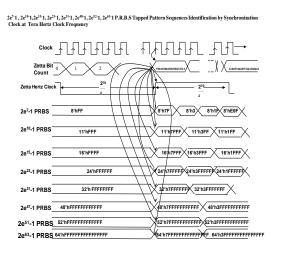

The Pseudo Random Data Framer Array Encryption and Decryption is mainly used for Encrypted and Decrypted the Randomized Data for all wireless and telecom, cryptographic Data Security and Data Communication and Networking Protocol Computing applications and products. The main aim of the design is to Pseudo Random binary Sequence Pattern Serial and Parallel Data Encryption and Decryption for identification of Property of Pseudo Random binary Sequence SEED WORD Patterns  $-2e^{7-1}$ ,  $2e^{10-1}$ ,  $2e^{10-1}$ ,  $2e^{23-1}$ ,  $2e^{31-1}$ ,  $2e^{48-1}$ ,  $2e^{52-1}$ ,  $2e^{52-1}$ ,  $2e^{63-1}$ ,  $2e^{127-1}$ ,  $2e^{255-1}$  etc as per Single Precision and Double, Quad Data, Octal Data Array Precision Highly Stringent Data Standards of Different High Speed Data w.r.t ultra High Clock Frequencies Synchronization- Mega, Giga, Tera, Peta, Exa, Zetta, Yotta, Xona, Weka, Vendica Hertz and also Data Speed in terms of Data Bytes, Frames, Super Frames, Very Long word Frames, Super Very long Word Frames, Data Packets, Internet Data Packets and Baud Rate in terms Mega, Giga, Tera, Peta, Exa, Zetta, Yotta, Xona, Weka, Vendica Bits/ Bytes per Second and PRBS Data Encryption and Decryption Memories are in terms of Mega, Giga, Tera, Peta, Exa, Zetta, Yotta, Bronto, Geop Bytes, Frames, Super Frames, Very long Super Word Frames, large array randomized data packets and words for parallel Distributed Computing Data Processing and Storage, execution o f Internet data packets, Cloud /Cluster Data Computing Processing and storage ,execution purpose. All these different groups of P.R.B.S L.F.S.R Frame Array Registers  $10e'_{-}$ 1,10e<sup>10</sup>-1,10e<sup>15</sup>-1,10e<sup>31</sup>-1,10e<sup>48</sup>-1,10e<sup>52</sup>-1,10e<sup>63</sup>-1, 10e<sup>127</sup>-1, 10e<sup>255</sup>-1 Frame array groups with different process tapping elements (7,6),(10,7),(14,15),(28,31)(42,47),(48,51),(57,63),(123,127)(247,255) are processed in the form of parallel and independently for improvement of speed and performance, reduction of very less time delay and complexity of the design. The Intention is for Hi-Fi Industrial Standard P.R.B.S Data Framer Array A.S.I.C S.O.C Soft I.P Core Design as per C.C.I.T.T-I.T.U O.150/O.151/O.152/O.153 Software Industry Standards, and Software Design implementation using V.H.D.L & Verilog H.D.L Coding, Programming and

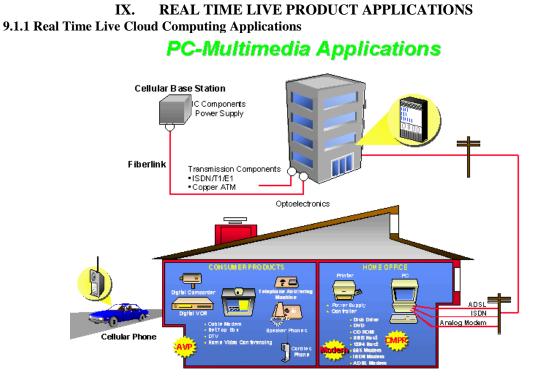

Debugging done using F.P.G.A –Xilinx 3s4000lfg900-4 . This A.S.I.C is mainly used for processing Parallel Pipelined Distributed Array Data Computing /Cloud Computing for Large High Speed Long Distance Wireless Communication Data Computing Products (Long Terminal Equipment –A.S.I.C) like Cloud Data Computing Wireless Network Stations/Shells, Advanced Distributed Processor Array Computing Products / Applications like 3G, 4G, 5G, 6th sense Processing and Computing. Of large big data.

In Hi-tech Smart Digital Computing Software World, So many advanced smart wireless, consumer mobile and internet cloud computing on chip based products and Parallel Distributed Processor Array based Computing Products came to the market like advanced eepads, notepads, tablets, iphones, Pocket Mobile Multimedia Computer, GPS Mobile Computer, Parallel Pipelined Array Based Distributed Computing Based Processors and Graphics Processors, Smart wireless network on chips ,WiFi,GiFi,WiMAx, and system on chip based wireless products , advanced portable handheld electronic instrument products, because of high speed wireless data packets processing and computing, transmission and reception in terms of Giga bits per second (Gbps) baud rate synchronizing with clock and time. According Current Market Trends , I Designed P.R.B.S Framer Array A.S.I.C SOC Soft I.P Core Designed for High Speed Computation in terms of Tera / Peta / Exa / Zetta /Yotta/Xona/Weka Hertz frequency baud rate( bits per Second) based wireless ,consumer, Medical, Image and Video Processing, avionics, space communication based High Speed Data Computation purpose. In Hi-tech Smart Computing Real Time Digital Industrial World & Hi-tech Real time Software Computing World, Every item is smart computing w.r.t speed, power, potential, frequency, Size, performance, Reliability according to Electronic Design and Software Quality Standards.

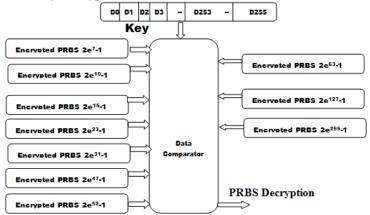

The Pseudo Random Binary Sequence Array A.S.I.C consists of 32 P.R.B.S Registers out of 32 Registers PRBS LFSR Registers-  $2e^{7}$ ,  $2e^{10}$ -1,  $2e^{15}$ -1,  $2e^{18}$ -1,  $2e^{23}$ -1,  $2e^{31}$ -1,  $2e^{63}$ -1,  $2e^{127}$ -1,  $2e^{255}$ -1 of each Four Register Array, Each of the Four Register form Frame Array Group, The Multiple P.R.B.S Framer Array A.S.I.C Products Integrated to form multiple framer arrays of Different P.R.B.S L.F.S.R Registers with Different Tapping Elements 8,16,32,64,128,256 Bit of Different Random Pattern Sequences 2e<sup>7-1</sup>,2e<sup>10</sup>-1,2e<sup>15-1</sup>,2e<sup>31</sup>- $1,2e^{-63}-1,2e^{127}-1,$  $2e^{255}-1$ with tapping point (7,6),(10,7),(14,15),(28,31)(42,47),(48,51),(57,63),(123,127)(247,255) of different data frame arrays and lengths. P.R.B.S A.S.I.C S.O.C processing multiple array of frames of data at a time processed and computing by implementation parallel distributed pipelined array computing technique for data fetching and decoding and executing large data frames for particular application/product This is an single chip Universal ASIC S.O.C Solution for all products and applications like wireless and telecom, bus data communication and networking, cloud and internet computing, super Grid/Cluster/Parallel Distributed computing solutions, consumer and mobile smart digital electronics, satellite and space, aerospace engineering, automotive applications and products.

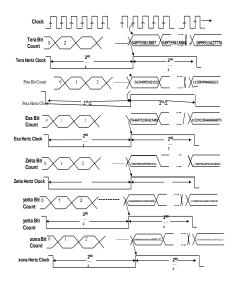

I' Designed and Implemented the product for parallel Distributed Array Processor Computing based Products and Applications for Transmission and Reception and Processing of Data in High Speed Computing in the form of P.R.B.S Data Packets and Frames. The main intension the design is for Highly Reliable w.r.t complexity, performance and size and power consumption. At a time process the 8 x 4 Frames of data processing and computing by synchronizing with single clock pulse w.r.t different High Data Frequency Clock Rates in terms of Tera, Peta, Exa, Zetta, Yotta, Xona, Weka Baud Rates. This P.R.B.S Framer Array A.S.I.C is very suit for all universal processing products and applications Specific to Parallel Distributed Pipe lined Array Processing Computers for processing and computing the instruction and data fetching, decoding, executing randomly in repeated number of times according to tapping processing elements at very high frequency rates in terms of Tera , Peta, Exa , Zetta , Yotta, Xona , Weka Hertz Clock Frequency Baud Rates. This P.R.B.S Framer Array A.S.I.C is for computing and processing the large Complex Cloud data computing in the form of Frame Arrays 32 frames at a time for large computational data based applications and products at very high frequency baud rates - Tera, Peta, Exa, Zetta, Xona, Yotta, Weka Hertz Clock Frequency. Also the P.R.B.S Framer is for processing and computing the Large Image, Video, Graphics, Medical Diagnostic Images and products at a very high speed w.r.t baud rate speed in terms of above mentioned frequencies by synchronizing with Single Clock. The PRBS Framer Array Processing the Large Data Frames for Hi-Fi Electronic Design Automation products Avionics as per D.O-178 Software standards, Automotive as per I.E.C-50128/9,60128 C.E.N.L.E.C Standards. I' Implemented the P.R.B.S Framer Array A.S.I.C S.O.C Design using Parallel Distributed Pipeline Array Computing Technique for fetching, decoding, executing all random data frame arrays. these random seed word frames processed in the form of parallel groups, the advantages are save more number of data frame array packets, reduction of multiple IO Ports, and number of Data shift Registers, improvement of Processing speed, all these data seed words are repeated number of times w.r.t data width. For example 10e<sup>7</sup>-1 PRBS – LFSR Register, the length of randomized data width is 2<sup>L</sup>-1. Similarly other PRBS Random Pattern Sequences 10e<sup>10</sup>-1,10e<sup>15</sup>-1,10e<sup>31</sup>-1 of different tapping elements. The product is very suit for processing large data packets in the internet data computing and cloud computing, processing speed is very high and also this product is very suit for reduction of internet data packets frame array traffic errors and reduction of noise, eliminating internet data

packets traffic loss. This saves more processing time delay, reduction of more hardware complexity and size on the cards/boards due to this S.O.C. This product is also very suit for processing and computing large data frames at a time without any data loss in cloud computing and network racks and stations ,server arrays. This reduces more processing delay time, easy debug process, flexible and compatible, more reliable of real time data computing. Switching of data frames is so easy , because of I developed parallel processing and computing data technique. This product is operated with different clock frequencies – Tera, Peta, Exa, Zetta, Yotta, Xona, and Weka Hertz Clock Frequency Baud Rates for very high speed processing . Instead of using multiple PRBS Transceivers , I Implemented in the single P.R.B.S Framer Array A.S.I.C S.O.C IP Core. And this product mainly intended for very high long distance communication purpose. For avoidance of traffic data collision and loss of data packets, also for clean digital data without unwanted spikes / noise occurred while doing transmission and reception, I used Parallel Distributed P.R.B.S Framer Array A.S.I.C IP Core.

This product is not only suit for Cloud and internet data computing E.D.A applications/products, this P.R.B.S Framer A.S.I.C Array also suit for various electronic applications/products like Graphics Processing and Animation, Image and Video data Processing (Digital Cameras), Cryptography applications, S.O.C Design data Testing by processing of Random Array Data Frames, Smart Real time Digital Consumer Mobile and Multimedia Electronic Data Processing, large wireless and telecom data communication engineering applications and also for space, satellite, aerospace, automotive data processing products and applications. In Image processing, all the pixel data array frames data processed in the form of data frame windows by using PRBS Framer Array A.S.I.C. Very less time takes to scan the window frames in the form of vertical and horizontal lines and frames format. In SOC Testers also this product dominates lot compared to other testing techniques like Boundary Scan Array S.O.C, Logic B.I.S.T and B.I.L.B.O Arrays. Testing Speed is so very high and also at a time scanning and testing multiple large data frame arrays using the product, simply this product test multiple S.O.C's at a time. This product also very suit for Very High Advanced High Speed Serial and parallel Data Communication Protocols - R.S 232,485,U.A.R.T ,U.S.B 2.0,3.0,P.C.I,S.A.T.A Frame Arrays processing and Computing while transmission and reception of long distance communication protocol applications and products. Also this product is very suit for processing data in Network on Chip Computing based Wi-Fi router ASIC products. Not only communication applications, this product is very suit for Aerospace and satellite vehicles for processing and computing large data frames in the form of parallel computing without any data loss and miniature catastrophic data failures and very less noise. This product is very highly reliable and complete Quality soft A.S.I.C IP Core Product.

#### II. P.R.B.S DATA FRAMER ARRAY, ENCRYPTION AND DECRYPTION DESIGN ARCHITECTURES

#### P.R.B.S Data Encryption & Decryption Diagram of different P.R.B.S Patterns

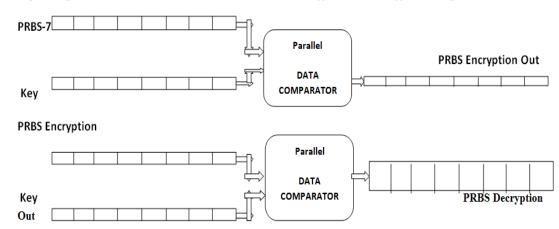

Logic Design Architecture – Serial and Parallel PRBS Data Encryption and Decryption Design Architecture

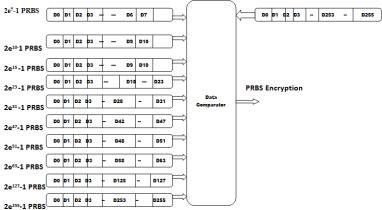

This A.S.I.C Soft I.P Core Design Module of P.R.B.S Data Encryption and Decryption basically consists multiple P.R.B.S Designs of different Pattern sequence lengths  $-2e^{7-1}$ ,  $2e^{10-1}$ ,  $2e^{15-1}$ ,  $2e^{23-1}$ ,  $2e^{31-1}$ ,  $2e^{48-1}$ ,  $2e^{52-1}$ ,  $2e^{63-1}$ ,  $2e^{127}$ ,  $1, 2e^{255}$ -1 are processed randomized Data frequencies and numbers are in parallel for advanced Digital Smart Parallel Distributed Computing A.S.I.C and Internet, Cloud/cluster Soft IP Core computing products and applications in advanced Data Communication and Networking Protocol soft I.P Cores /Cards and Serializer and Deserializers, Data interface Cards, Advanced A.S.I.C and F.P.G.A Application Cards/Boards or S.O.C Designs and Secure Data Communication and Cryptography Applications . etc Due to

this we can easily interface data randomly w.r.t data design cards of different length of bits and Different speed rate in terms of Data bytes, words, frames, super frames, super word frames, packets etc.

Fig 1.0 PRBS Data Framer Array Encryption

A. PRBS Data Framer Array Decryption

Fig 1.1 PRBS Data Framer Array Decryption

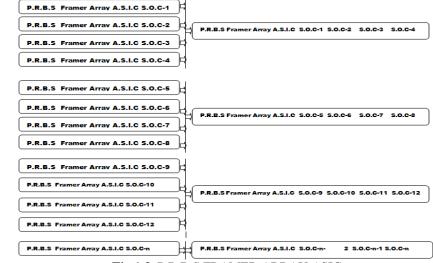

B. P.R.B.S Framer Array ASIC S.O.C Architecture

#### C. Description

The Pseudo Random Binary Sequence Array ASIC consists of 32 PRBS Registers out of 32 Registers PRBS LFSR Registers- 2e<sup>7</sup>-1, 2e<sup>10</sup>-1, 2e<sup>15</sup>-1, 2e<sup>18</sup>-1,2e<sup>23</sup>-1, 2e<sup>31</sup>-1, 2e<sup>63</sup>-1, 2e<sup>127</sup>-1, 2e<sup>255</sup>-1 of each Four Register Array, Each of the Four Register form Frame Array Group, The Multiple P.R.B.S Framer Array A.S.I.C Products Integrated to form multiple framer arrays of Different P.R.B.S L.F.S.R Registers with Different Tapping Elements 8,16,32,64,128,256 Bit of Different Random Pattern Sequences 2e<sup>7-1</sup>,2e<sup>10</sup>-1,2e<sup>15-1</sup>,2e<sup>31</sup>-1,2e<sup>63</sup>-1,2e<sup>127</sup>-1, 2e<sup>255</sup>-1 with tapping points (7,6) ,(10,7),(14,15),(28,31),(58,63),(126,127),(253,255) of different data frame arrays and lengths. P.R.B.S A.S.I.C S.O.C processing multiple array of frames of data at a time processed and computing by implementation parallel distributed pipelined array computing technique for data fetching and decoding and executing large data frames for particular application/product This is an single chip Universal ASIC S.O.C Solution for all products and applications like wireless and telecom, bus data communication and

networking, cloud and internet computing, super Grid/Cluster/Parallel Distributed computing solutions, consumer and mobile smart digital electronics, satellite and space, aerospace engineering, automotive applications and products.

### D. Universal P.R.B.S Super Frame Array ASIC S.O.C Design Architecture

Fig.1.3. P.R.B.S FRAMER ARRAY ASIC

#### E. Description

The Above Architecture Consists P.R.B.S Framer Array A.S.I.C S.O.C 1,2,3,4 ----- 10,12,13,14 , ----n-3,n-2,n-1,n are grouped and divided in to P.R.B.S Framer Array A.S.I.C S.O.C Very long word Super Frame Array packets Format. All integrated form multiple very long word super frame array packets A.S.I.C S.O.C Architecture. All such super frames again grouped and integrated to form very long word super frame array a.S.I.C S.O.C Architectures for processing and computing multiple Cloud Array and Internet array computing solutions using these products. All the very long word super framer array data packets processed in the form of parallel pipelined array computing ,for large computing data applications, at a very high speed and long distance communication purpose, For high speed I am using Giga, Tera ,Peta , Exa, Zetta, Xona, Weka, Vendica, 2<sup>1000</sup>, etc Super frame carrier synchronous Clock frequencies with accurate data communication without any data packets loss and internet traffic loss, this product is very futuristic and even this engineering soft IP Core product is not available in the world market, may be hundreds of years time takes this product will come to the market in the major fortune, now I designed with highly intelligence logic design implemented through software code.

#### IV. FORMULAS – PSEUDO RANDOM BINARY SEQUENCE POLYNOMIALS

|      |              | $= 1 + x^6 + x^7$         |      |

|------|--------------|---------------------------|------|

|      |              | $= 1 + x^3 + x^{10}$      | (2)  |

|      |              | $= 1 + x^{14} + x^{15}$   | (3)  |

|      |              | $= 1 + x^{18} + x^{23}$   | (4)  |

|      |              | $= 1 + x^{28} + x^{31}$   | (5)  |

| PRBS |              | $= 1 + x^{42} + x^{47}$   | (6)  |

|      |              |                           | (7)  |

|      | $2e^{63}-1$  | $= 1 + x^{58} + x^{63}$   | (8)  |

|      | $2e^{127}-1$ | $= 1 + x^{123} + x^{127}$ | (9)  |

| PRBS | $2e^{255}-1$ | $= 1 + x^{247} + x^{255}$ | (10) |

|      |              |                           |      |

#### V. CLOCK SYNCHRONIZATION WAVE FORM DIAGRAMS

#### VI. P.R.B.S TELECOM FREQUENCY STANDARD TABLE

| PRBS TYPE            | STANDARD                | SUGGESTED DATA RATE (Kilo Bits       | FEED BACK TAP |  |  |  |

|----------------------|-------------------------|--------------------------------------|---------------|--|--|--|

|                      |                         | Per Second)                          |               |  |  |  |

| $2e^{7}-1$           | ITU-T O.150             | 14.4                                 | 7,6           |  |  |  |

| $2e^{10}-1$          | ITU-T O.150             | 64                                   | 10,3          |  |  |  |

| $2e^{15}-1$          | ITU-T 0.151             | 1544, 2048, 6312, 8448, 32064, 44736 | 14,15         |  |  |  |

| $2e^{23}-1$          | ITU-T O.150             | 34368, 44736, 139264                 | 18,23         |  |  |  |

| $2e^{31}-1$          | ITU-T 0.150             | 1.2,1.5 G .b.p.s                     | 28,31         |  |  |  |

| $2e^{48}-1$          | ITU-T O.150/151/152     | 500 G.b.p.s                          | 48,42         |  |  |  |

| $2e^{52}-1$          | ITU-T O.150/151/152     | 1 T.b.p.s                            | 52,47         |  |  |  |

| $2e^{63}-1$          | ITU-T O.150/151/152/153 | 500 T.b.p.s                          | 48,63         |  |  |  |

| 2e <sup>127</sup> -1 | ITU-T O.150/151/152/153 | 1 P.b.p.s                            | 123,127       |  |  |  |

| $2e^{255}-1$         |                         | 500 P.b.ps and 1 E.b.p.s             | 247,255       |  |  |  |

| -                    | 1 4 555 6 5             |                                      |               |  |  |  |

Table.1. PRBS Pattern Sequences as per ITU O.150/O.151/O.152 Standards

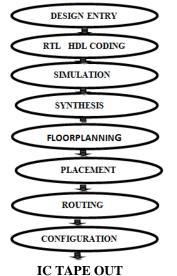

# VII. VLSI – IC F.P.G.A SOFTWARE I.P CORE – P.R.B.S FRAMER ARRAY A.S.I.C. S.O.C DESIGN FLOW CHART

Fig1.4: VLSI IC EDA Software Design Flow

#### 7.1.1 Description

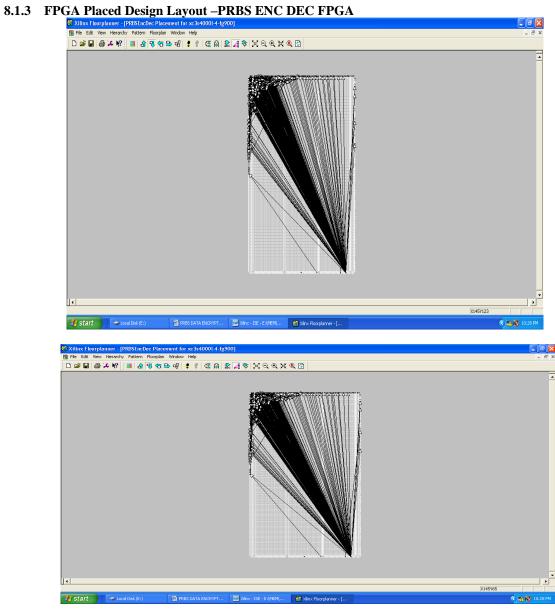

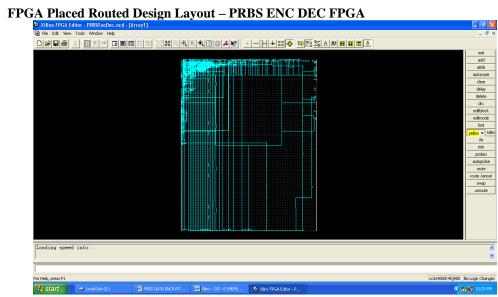

This is Standard Industry Design Flow Chart for Delivery of VLSI IC Chip Design Soft IP Core Products/Designs. Initially entering RTL Design of P.R.B.S Framer A.S.I.C S.O.C I.P Core through Design Entry Step, After That RTL VHDL & / Verilog HDL Coding Done through HDL RTL Design Software Editor of both behavioral and Data flow models using Xilinx ISE Software . Verification & Running the Functionality of RTL HDL Design Description through by Simulation and Abstract the Description in to Gate Level Net list

using Synthesis, subsequently Place & Routing through FPGA Placed Design & Router and Programming and Debugging Done through Reconfiguration using JTAG Debugger. All the Design flow reports generated by using Xilinx ISE 10.1i ISE Software Design Tool. This Design Flow Estimates the number of Placed Design Blocks and Routing Paths (Number of Routing Wires connected on F.P.G.A). This Xilinx ISE FPGA Design Flow not only estimates placed and routed design components on FPGA, also estimates number of clocks, static timing, power ,performance , speed, mapping before and after, pre and post simulation and synthesis, Floor planning of hardware P.R.B.S. Framer Array A.S.I.C S.O.C I.P Core etc.

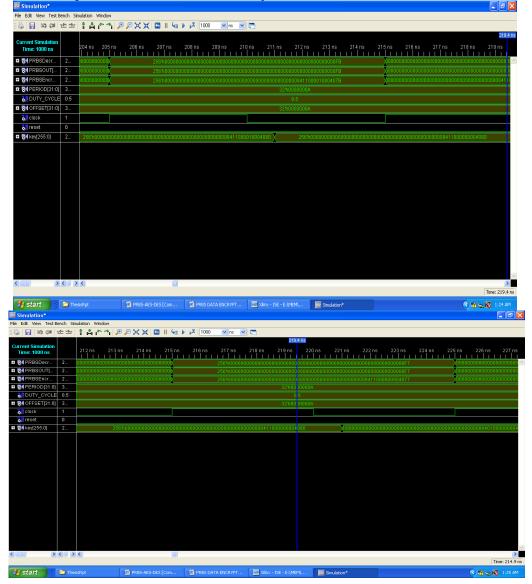

#### VIII. FPGA INDUSTRIAL DESIGN FLOW REPORTS 8.1.1 Simulation Reports – PRBS Data Framer Array

Ultra High Multi Clock Frequency Spectrum -Zetta, Yotta, Xona, Weka Hertz Real Time Clock...

Ultra High Multi Clock Frequency Spectrum -Zetta, Yotta, Xona, Weka Hertz Real Time Clock...

| Simulation                          |            |                       |                     |                         |                      |                    |                    |                     |                    |

|-------------------------------------|------------|-----------------------|---------------------|-------------------------|----------------------|--------------------|--------------------|---------------------|--------------------|

| ile Edit View TestB                 |            |                       |                     |                         |                      |                    |                    |                     |                    |

| 炎 🔚 🖄 🌒                             | ±±±r       | ተልሶኅ 🕫 🔎              | X X 🖬 II 🗐 🕨        | 🖌 🔽 1000 🔽 ns 💌         | <b>1</b>             |                    |                    |                     |                    |

| Current Simulation<br>Time: 1000 ns |            | 112500 ps 115000 ps   | 117500 ps 12        | 0000 ps 122500 ps       | 125000 ps 127500 p   | ps 130000.ps 13    | 12500 ps 135000 ps | 137500 ps 140       | 000 ps 142500 ps   |

| PRBSOUT[                            | 6          | 64'h00000000000000000 | 64'h000000000000000 | 03(64'h0000000000000007 | 64'h0000000000000000 | 64h000000000000000 | 64h00000000000003F | 64h0000000000000007 | FXh000000000000000 |

| RBSEncr                             | 8'h96      | 8'h54                 | 8'h56               | 8'h52                   | 8115A                | 8'n4A              | 876A               | 8ħ2A                | 8'hAB              |

| RBSDecr                             | 8'nC3      | ( 8'n01 )             | 8%D3                | 8'h07                   | 870F                 | 811F               | 8113F              | 8h7F                | 8'hFE              |

| Neriod(31:0)                        |            |                       |                     |                         | 32'h00000            | 0004               |                    |                     |                    |

| DUTY_CYCLE                          |            |                       |                     |                         |                      |                    |                    |                     |                    |

|                                     |            |                       |                     |                         | 32%00000             | A000               |                    |                     |                    |

| 引 clock                             | 1          |                       |                     |                         |                      |                    |                    |                     |                    |

| 3.∏ reset 5.¶ key[7:0]              | 0<br>8'h55 |                       |                     |                         | 8'h55                |                    |                    |                     |                    |

|                                     |            |                       |                     |                         |                      |                    |                    |                     |                    |

|                                     | < } >      | K                     | <u> </u>            |                         |                      |                    |                    |                     | Time:              |

| y start                             | 🍲 Loca     | l Disk (E:)           | RB5 DATA ENCRYPT    | Xlinx - ISE - E:\MEM(   | Simulation           |                    |                    |                     | < 🖍 🔣 10:24 P      |

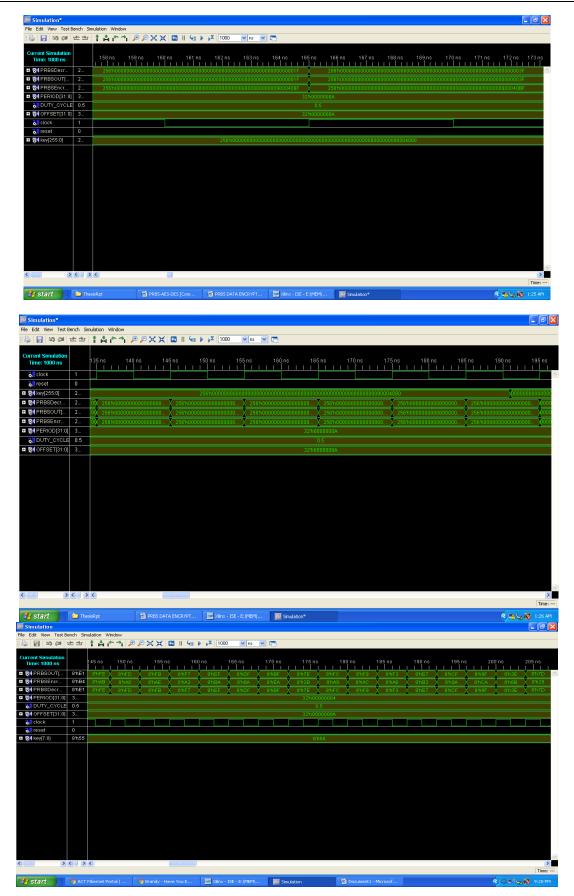

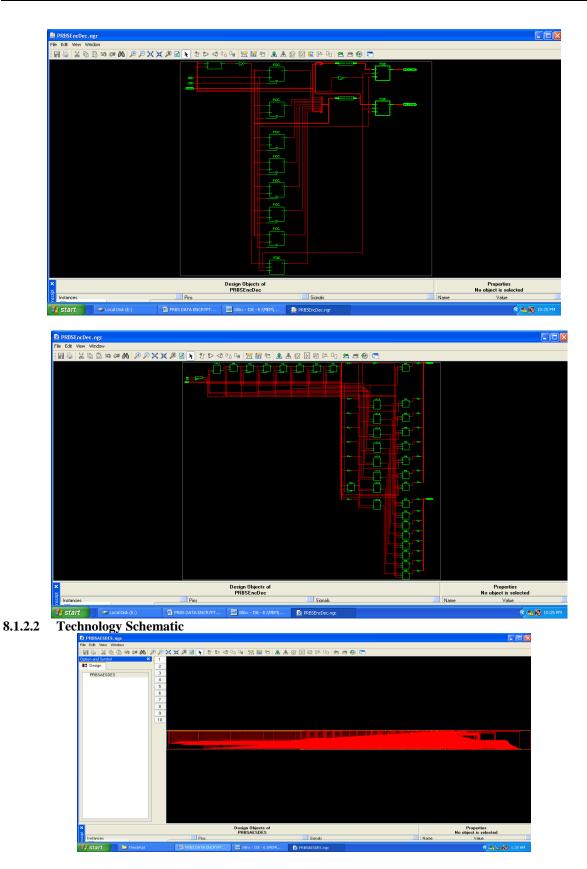

8.1.2 R.T.L. Design Blocks & Schematics - PRBS Data Framer Array Encryption and Decryption 8.1.2.1 R.T.L Top Level Block

| RBSAESDES.ngr<br>File Edit View Window |                        |                                                        |                                                                           |         |                              |

|----------------------------------------|------------------------|--------------------------------------------------------|---------------------------------------------------------------------------|---------|------------------------------|

|                                        | M /# /# X X /#  #      | 1 💽 🕸 🗇 🕫 🗣 🔀 🔠 🏦                                      | A D D 💫 🗠 🗤 🕿 🕿 😧 🗂                                                       |         |                              |

|                                        |                        |                                                        |                                                                           |         |                              |

| _                                      |                        |                                                        |                                                                           |         |                              |

|                                        |                        |                                                        |                                                                           |         |                              |

|                                        |                        |                                                        |                                                                           |         |                              |

|                                        |                        |                                                        |                                                                           |         |                              |

|                                        |                        | key(255:0)                                             | PRBSDecr(255:0)                                                           |         |                              |

|                                        |                        |                                                        |                                                                           |         |                              |

|                                        |                        |                                                        |                                                                           |         |                              |

|                                        |                        | clock                                                  | PRBSEncr(255:0)                                                           |         |                              |

|                                        |                        | CIOCK                                                  |                                                                           |         |                              |

|                                        |                        |                                                        |                                                                           |         |                              |

|                                        |                        |                                                        |                                                                           |         |                              |

|                                        |                        | reset                                                  | PRBSOUT(255:0)                                                            |         |                              |

|                                        |                        |                                                        |                                                                           |         |                              |

|                                        |                        |                                                        |                                                                           |         |                              |

|                                        |                        |                                                        |                                                                           |         |                              |

|                                        |                        |                                                        |                                                                           |         |                              |

|                                        |                        |                                                        |                                                                           |         |                              |

| ×                                      |                        | Design Objects of<br>Top Level Symbol                  |                                                                           | Propert | ties of Instance<br>BSAESDES |

| Instances                              |                        | Pins                                                   | Signals (                                                                 | Name    | Value                        |

|                                        |                        | S DATA ENCRYPT 🛛 🔤 Xilinx - ISE - E:\MEM\              | PRBSAESDES.ngr                                                            |         | 🔦 🌇 😓 🔞 1:27 AM              |

| 🛃 start 🔰 💈 🗀 ThesisF                  | Rpt 🔤 PRB              |                                                        | · B HKDSAESOESING                                                         |         |                              |

| BSEncDec.ngr                           | Rpt 🔟 PRB              |                                                        | · · · · · · · · · · · · · · · · · · ·                                     |         |                              |

| BSEncDec.ngr                           | Rpt 👘 PRB              |                                                        | n 📑 Prosecoos.ngr                                                         |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        |                                                        | <ul> <li>■ Incalaciany</li> <li>▲ IS IS IS IS 14 00 (55 5 (6))</li> </ul> |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        |                                                        |                                                                           |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        |                                                        |                                                                           |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        |                                                        |                                                                           |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        |                                                        |                                                                           |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        |                                                        |                                                                           |         |                              |

| BSEncDec.ngr<br>lit View Window        |                        | ▲ 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                | ▲☆⊠≋⊨□≤≠⊕©                                                                |         |                              |

| BSEncDec.ngr<br>lit View Window        |                        | ▲ 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                | ▲☆⊠≋⊨□≤≠⊕©                                                                |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        |                                                        |                                                                           |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        | ▲ 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                | ▲☆⊠≋⊨□≤≠⊕©                                                                |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        | • ま⊳⊲ ₀ ҹ ⊠ ⊠ ๒ ≵<br>— key(7:0)                        | ▲☆⊠≋⊨□≤≠⊕©                                                                |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        | • ま⊳⊲ ₀ ҹ ⊠ ⊠ ๒ ≵<br>— key(7:0)                        | ▲☆⊠≋⊨□≤≠⊕©                                                                |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        | ▲ 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                | ▲☆⊠≋⊨□≤≠⊕©                                                                |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        | • ま⊳⊲ ₀ ҹ ⊠ ⊠ ๒ ≵<br>— key(7:0)                        | ▲☆⊠≋⊨□≤≠⊕©                                                                |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        | • ま⊳⊲ ₀ ҹ ⊠ ⊠ ๒ ≵<br>— key(7:0)                        | ▲☆⊠≋⊨□≤≠⊕©                                                                |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        | • ± ▷ < 0 • • • • • • • • • • • • • • • • • •          | PRBSDecr(7:0)                                                             |         |                              |

| BSEncDec.ngr<br>lit View Window        |                        | • ま⊳⊲ ₀ ҹ ⊠ ⊠ ๒ ≵<br>— key(7:0)                        | ▲☆⊠≋⊨□≤≠⊕©                                                                |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        | • ± ▷ < 0 • • • • • • • • • • • • • • • • • •          | PRBSDecr(7:0)                                                             |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        | • ± ▷ < 0 • • • • • • • • • • • • • • • • • •          | PRBSDecr(7:0)                                                             |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        | • ± ▷ < 0 • • • • • • • • • • • • • • • • • •          | PRBSDecr(7:0)                                                             |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        | • ± ▷ < 0 • • • • • • • • • • • • • • • • • •          | PRBSDecr(7:0)                                                             |         |                              |

| BSEncDec.ngr<br>dit View Window        |                        | • ± ▷ < 0 • • • • • • • • • • • • • • • • • •          | PRBSDecr(7:0)                                                             |         |                              |

| RBSEncDec.ngr<br>Edit View Window      |                        | ★ tr ▷ < to □ = to | PRBSDecr(7:0)                                                             |         |                              |

| RBSEncDec.ngr<br>Edit View Window      |                        | • ± ▷ < 0 • • • • • • • • • • • • • • • • • •          | PRBSDecr(7:0)                                                             |         | Prometilies of Instance      |

| RBSEncDec.ngr<br>Edit View Window      | ₽₽ <b>¥</b> ¥ <b>₽</b> | key(7:0) clock reset                                   | PRBSDecr(7:0)                                                             | Nane    |                              |

- 2.2953A505.ppg Re fait wer woodw [回』》 び 応 応 ち ゆ & | ア ア ズ ズ ゆ 図 尾 か ひ ム 毕 卓 [ 25 編 で ] 魚 木 の 図 前 下 っ ! 生 中 ④ 同 3 4 5 6 Û Ű 12 12 0 <u>ت</u> Û Ð Õ ÷ Ũ Õ Ű Design Objects of PRBSAESDES Properties No object is selected Name Signals Pins 155 👮 PRE PRBSAESDES.ngr File Edit View Window 5 | 💥 🖻 🖆 🚧 📣 🔎 🔎 🗙 🗶 🔎 🖻 💊 🎌 ▷ < % 🐄 🔀 🔠 🕭 🛦 🕸 🔯 🗞 🕿 🖻 🛞 3 4 5 Design Objects of PRBSAESDES Properties No object is selected Signals Name Pins Instances Value 🛃 start 🔰 🕻 🚞 Thes PRBS DATA ENCRYPT... 🕅 Xlinx - ISE - E:\MEM\... 🛃 PRBSAESDES.ngr C 🛝 😹 🕸 🗉 PRBSAESDES.ngr File Edit View Window ◼▯▯▯▯▯▯▯▮◢ਸ਼©©, װױױﻩ ◊ﻩױ, װױָר אַפּר װ 4 Design Objects of PRBSAESDES Properties No object is selected Signals Name Pins 🔇 🐴 😓 🔞 1:27 AM 1 RBSAESDES.r

- 8.1.2.1 **R.T.L Schematic**

| PRBSAESDES.ngc        |                                               |                                     |

|-----------------------|-----------------------------------------------|-------------------------------------|

| File Edit View Window |                                               |                                     |

|                       | 🖻 🔎 🗶 🗶 🕼 🕼 🕼 🐂 🔀 🏗 🖆 🏦 🛦 🕼 🔯 🖳 🗠 🗮 🚱 🔚       |                                     |

| Option and Symbol X   | 1                                             |                                     |

| E Design              | 2                                             |                                     |

| PRBSAESDES            | 3                                             |                                     |

|                       | 4 5                                           |                                     |

|                       | 5                                             |                                     |

|                       | 7                                             |                                     |

|                       | 8                                             |                                     |

|                       | 3                                             |                                     |

|                       | 10                                            |                                     |

|                       |                                               |                                     |

|                       |                                               |                                     |

|                       |                                               |                                     |

|                       |                                               |                                     |

|                       |                                               |                                     |

|                       |                                               |                                     |

|                       |                                               |                                     |

|                       |                                               |                                     |

|                       |                                               |                                     |

|                       |                                               |                                     |

|                       |                                               |                                     |

|                       |                                               |                                     |

|                       |                                               |                                     |

|                       |                                               | -                                   |

| ×                     | Design Objects of<br>PRBSAESDES               | Properties<br>No object is selected |

| Instances             | Pine Signale                                  | Name Value                          |

| 🐈 start 📄 🎦 ThesisRot | D PRBS DATA ENCRYPT De EtMEM D PRBSAESDES.noc | C                                   |

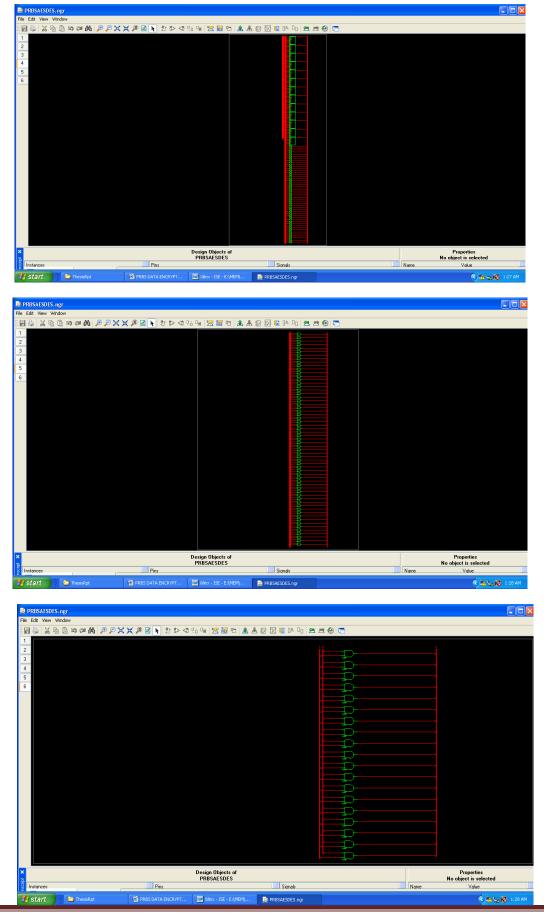

#### 8.1.4

|                                                 | ravelineCDLEDIsvClokgenvClokgen.ise - [F                         | RBSDataEncrypDecryp.v]            |                       |                         |              |

|-------------------------------------------------|------------------------------------------------------------------|-----------------------------------|-----------------------|-------------------------|--------------|

| 📝 File Edit View Project Source Process         | · Window Help<br>  😂 @비 🕗 🗄 🔑 🔎 그녀 💥 🔎 💽 🍃                       | S = 6 N2 = A N2                   |                       | 0+ 0+ 0+                |              |

| :                                               |                                                                  |                                   |                       | e4 ×4 ≠4                |              |

| Sources                                         |                                                                  |                                   |                       |                         |              |

| Sources for: Implementation                     | 1 `timescale ins /<br>2 module PRBSEncDec                        | lps<br>c(clock,reset,key,PRBSOUT  | (,PRBSEncr,PRBSDecr); |                         | ^            |

| - Clokgen                                       | 3 input clock.reset                                              |                                   |                       |                         |              |

|                                                 | \MEM\onetotenclkdrv\BINBCDLEDis\clok                             | gen\PRBSEncDec.ucf                |                       |                         | _            |

|                                                 | s Areas Tools Window Help                                        |                                   |                       |                         |              |

| M GIVINGION (1 1)                               | ю <b>н </b> ≁ №?                                                 |                                   |                       |                         |              |

| 🖵 💟 multickpt 👔 Design Browse                   | r 🗖 🗖 🔀                                                          | Device Architecture for xc        | 3s40001-4-fg900       |                         |              |

| 🕡 🔁 1/0 Pins                                    |                                                                  |                                   |                       | <u> </u>                |              |

|                                                 |                                                                  |                                   |                       |                         |              |

|                                                 |                                                                  |                                   |                       |                         |              |

| Processes                                       | >                                                                |                                   |                       |                         |              |

| Processes for: PRBSE                            | List - I/O Pins 📃 🗖 🔀                                            |                                   |                       |                         |              |

| Create<br>Floopl<br>Floopl<br>Floopl<br>Floopl  | Direction Loc Bank 1/0 (                                         |                                   |                       |                         |              |

| Floorpl Clock Ing                               | sut 🤤                                                            |                                   |                       |                         |              |

| 🖶 🍋 Synthesize 🗖 key[1] In:                     | ut                                                               |                                   |                       |                         |              |

| Key[2] Inj                                      | ut                                                               |                                   |                       |                         | ~            |

| Ef Processes key[4] In:                         | ut                                                               |                                   |                       |                         | >            |

| key(5) In;                                      |                                                                  |                                   |                       |                         |              |

| X<br>Started : key[7] in                        |                                                                  |                                   |                       |                         | ~            |

| key(9) In                                       | sut                                                              |                                   |                       |                         |              |

| key(10) inj<br>key(11) inj                      |                                                                  |                                   |                       |                         |              |

| Louit 91 Louit 91                               | <u> </u>                                                         | Package View Architecture View    | <u> </u>              | <b>▶</b> //             | ~            |

| E Console C Errors                              |                                                                  |                                   |                       |                         | >            |

| 🚊 📑 Console 🛛 Errors 🔔 Warnin                   | ngs 🚾 Tcl Shell 🐹 Find in Files                                  |                                   |                       |                         |              |

|                                                 |                                                                  |                                   |                       | GAPS NUM SCRL In 428 Co | 16 Verilog   |

| 🛃 start 🕴 🗢 Local Disk (E:)                     | PRBS DATA ENCRYPT 🔤 Xi                                           | Inx - ISE - E:\MEM\               | CE - E:\/MEM\         | < = 10                  | 10:34 PM     |

|                                                 | k                                                                |                                   |                       |                         |              |

| File Tools Help                                 |                                                                  |                                   |                       |                         | IÐ X         |

| Report Navigator ×                              | Name Power (W)                                                   | Used Total Available              | Utilization (%)       |                         |              |

| View                                            | Clocks 0.000                                                     |                                   |                       |                         |              |

| Report Views                                    | Logic 0.000 2                                                    | 33 55296                          | 0.4                   |                         |              |

| Summary<br>Thermal Information                  | Signals 0.000 5<br>IOs 0.000 2                                   | 63<br>58 633                      | 40.8                  |                         |              |

|                                                 |                                                                  |                                   |                       |                         |              |

| Settings                                        | Total Quiescent Power 0.264                                      |                                   |                       |                         |              |

| 😑 🌌 By Type                                     | Total Dynamic Power 0.000 Total Power 0.264                      |                                   |                       |                         |              |

| Clocks<br>Logic                                 |                                                                  |                                   |                       |                         |              |

| Signals                                         |                                                                  |                                   |                       |                         |              |

| IOs                                             |                                                                  |                                   |                       |                         |              |

| By Hierarchy                                    |                                                                  |                                   |                       |                         |              |

|                                                 |                                                                  |                                   |                       |                         |              |

|                                                 |                                                                  |                                   |                       |                         |              |

|                                                 |                                                                  |                                   |                       |                         |              |

|                                                 |                                                                  |                                   |                       |                         |              |

|                                                 |                                                                  |                                   |                       |                         |              |

|                                                 |                                                                  |                                   |                       |                         |              |

| Views                                           | Table View                                                       |                                   |                       |                         |              |

| and load the newly of                           | enerated PCF file into XPower                                    | Analyzer)                         |                       |                         |              |

| <ol><li>A post PAR simulation</li></ol>         | n-generated VCD or SAIF file i                                   |                                   |                       |                         | <u></u>      |

| frequencies                                     |                                                                  |                                   |                       |                         |              |

| 3. The clock frequency :<br>XPower Analyzer GUL | for clocks in the "Clocks By T<br>and then applying "Estimate Ac | ype" view in the<br>tivity Bates" |                       |                         |              |

| mover analyzer GUI                              | apprying ischwale AC                                             |                                   |                       |                         |              |

| Design 'PRBSEncDec.ncd' op                      | ened successfully                                                |                                   |                       |                         |              |

|                                                 |                                                                  |                                   |                       |                         |              |

|                                                 |                                                                  |                                   |                       |                         | ~            |

|                                                 |                                                                  |                                   |                       |                         | >            |

| Progress Report Warning Error                   |                                                                  |                                   |                       |                         |              |

| Ready                                           |                                                                  |                                   |                       |                         | APS NUM SCRL |

|                                                 |                                                                  |                                   |                       |                         |              |

| 🛃 Start 🔷 🗢 Local Disk (E:)                     | 🖬 PRES DATA ENCRYPT 🔤 XI                                         | inx - ISE - E:\MEM\ 🎆 Xfinx XF    | Power Analyze         | <b>(</b> ).             | 🔨 🔣 10:30 PM |

(intel)

Single-chip Cloud Computer

Labs has cre outer" (SCC) a Intel Architecture cores ever integrate chip – 48 cores. It incorporates technolo ale multi-core processors to 100 cores as an on-chip network, advanced powe hologies and support for "message-pas d on a s es a clo ad of a The novel many-cor or scalability in terms proved core-core cor e software to dynam y to attain power cor

equency to w as 25W. st achievement from Intel's Tera ch Program. The research was co ore, India. Intel Labs Braunschwei nts the latest achiever

Inside the Single-chip Cloud Computer The name "Single-chip Cloud Computer" reflects the fact that the architecture resembles a scalable cluster of computers such as you would find in a cloud, integrated rch chip feat

- 24 "tiles" with two IA cores per tile

A 24-router mesh network with 256 GB/s bisection bandwidth

- 4 Integrated DDR3 memory controlli

Hardware support for message-pass

Bringing the network closer to the user is key to 1000x

Ultra High Multi Clock Frequency Spectrum -Zetta, Yotta, Xona, Weka Hertz Real Time Clock...

Music

Stereo Headset with Bluetooth/UWB

60 GB HD

PC Sync

Imaging & Video

Biometrics

#### X. CONCLUSION

The Design is mainly Intended for increasing the speed of Data Frames and Mainly suit for Big Data base like Cloud, Internet data Computing Applications and Products

#### REFERENCES

- [1]. Khamer Fathima U B, Nandini, Vijay Ramprasad - Design and Implementation of E1 submultiframe (SMF) Formatter and Analyzer" 2011.

- [2]. Kevin Curran, Sean Carlin and Mervyn Adams "Security issues in cloud computing", published in August 2011, Elixir Network Engg.

- Friedman, A. A., & West D. M, (Oct. 2010) "Privacy and Security in Cloud Computing," Issues in Tech. Innovation. [3].

- Yau, S., S., & Ho G, (2010) "Protection of users' data confidentiality in cloud computing,"2nd Asia-Pacific Symposium on Internet [4]. ware

- M.Cluzeau. "Practical Data Communications", IEEE Trans. on Computers, 56(9): 1283-1291, 2007 [5].

- Cisco Systems, "Synchronous Digital Hierarchy (SDH) Graphical Overview", Oct 2006. [6].

- Wei-Zen Chen, Guan-Sheng Huang, "A Parallel Multi- pattern PRBS Generator and BER Tester for 40+ Gbps Serdes [7]. Applications", IEEE Asia-Pacific Conference on Advanced System Integrated Circuits, Aug 2004, pp. 318-321.

- [8]. "A design and analysis of SEED,"Press of Korea Information Security Agency, 2003.

- [9]. R.Clauberg "Data aggregation architectures for single chip SDH/SONET framers", IBM J. RES & DEV. VOL. 47 NO.2/3 March/May 2003.

- [10]. R.Clauberg "Data aggregation architectures for single chip SDH/SONET framers", IBM J. RES & DEV. VOL. 47 NO.2/3 March/May 2003.

- [11]. ITU-T, Recommendation G.707, -Network Node Interface for Synchronous Digital Hierarchyl, 2003.

- [12]. D. Bajic, J.Stojanovic, FTN Novi Sad, Fruskogorska, Mobtel Beograd, "Frame Alignment Monitoring For STM-1 Frame", IEEE International Conference on Communications, 2001. ICC 2001, Vol. 10, pp. 2953-2957.

- ITU-T Recommendation G.704 Synchronous frame structures used at 1544, 6312, 2048, 8448 and 44736 kbit/s hierarchical [13]. levels|.1998

- Zhang Xiaoru and Zeng Lieguang, "An SDH STM-1 termination IC", ASIC 2nd International Conference, pp 179-182, 1996 [14].

- [15]. F. Sinnesbichler, A. Ebberg, A. Felder, and R. Weigel, "Generation of high-speed pseudorandom sequences using multiplexing techniques,"IEEE Trans. Microw. Theory Tech., vol. 44, no. 12, pp. 2738-2742, Dec. 1996

- [16]. HDL Chip Design, Douglas J. Smith, Doone Publications, 1996

- R.N. Mutagi, "Pseudo Noise Sequences for Engineers", IEEE Electronics and Comm. Eng. Journal, April 1996 [17].

- [18]. D.W. Choi, "Frame Alignment in a Digital Carrier System - A Tutorial", IEEE Comm. Mag., pp. 47-54, Vol. 28, February 1990.

- ITU-T, Recommendation G.706, —General Aspects of Digital Transmission Systemsl, 1991. ITU-T Recommendation G.702, —Digital Hierarchy bit ratesl,1988. [19].

- [20].

- [21]. W Xu, Y Zhang, T Wood, The feasibility of launching and detecting jamming attacks in wireless networks, in ACM MOBIHOC;

Prof. P. N. V. M Sastry Currently working with a Capacity of Dean- IT EDA Software Industry CELL &

**R&D CELL & ECE** DEPARTMENT, He Did Master Degree In Science- M.S Electronics, Under Department Of Sciences, College Of Science & Technology AU -1998.Did PG Diploma In V.L.S.I Design, J.S.O.U.K.A.S Certified From V3 Logic Pvt Ltd, Bangalore-2001, Did M.Tech (ECE) From I.A.S.E Deemed University-2005. Currently Pursuing (Ph.D)-E.C.E(V.L.S.I) , J.N.T.U Hyderabad -2012 , Over Past 17 years of Rich Professional Experience with Reputed IT Software Industrial MNC's, Corporate -CYIENT

(INFOTECH), ISITECH as a world top keen IT Industrial Software Specialist – World Top Software Engineering Team Leader(Level 6) Eng-Eng- HCM Electronics Vertical & Sr. Program Manager -EDS,BT,NON BT Embedded Software ,Avionics & Automotive Hi-tech Software Engineering Verticals & Departments & I/C M.F.G Hi-tech Eng.Software Vertical , Program Lead – Embedded & VLSI & Engineering Delivery Manager – IT Semiconductor Software Engineering Vertical ,at ISiTECH , also worked with Govt R&D, Industrial Organizations, Academic Institutions of Comparative Designations & Rolls . His Areas Of Interest are V.L.S.I -V.H.D.L, Veirilog H.D.L, A.S.I.C, F.P.G.A & Embedded Software Product Architectures Design & Coding Development .He mentored & Architecting Various Real Time, R&D, Industrial Projects/Products related to VLSI & Embedded System Software & Hardware.. His Key Achievements are Participated Various Top Class International IT MNC Delegates Board Meetings, I.T Software M.N.C Board Meetings(Tier1/2 Level MRM-V.P,C.O.O Level), Guided R&D ,Industrial, Academic Projects /Products -VLSI-ASIC,FPGA & Embedded & Embedded, V.L.S.I Software Project &/ Program Coordinated Various In House & External IT Project Workshops & Trainings At Management & Also CYIENT( INFOTECH) as a I/C- MFG Eng Software Vertical, Also Participated Various National R&D Workshops, FESTS, FDP's &Seminars. Recently He Published Various 40 International Journals of Reputed Journals and Conferences also Certified Conference Chairs - ,I.T.C. I.D.E.S- MC GRAWHILL EDUCATION-Chennai & and Published 4 Journals at IEEE Computer Society and &I.E.E.E & I.E.E.E -C.S.N.T.-Gwalior & Best Paper Award On behalf of Exa Hertz Wi-Fi Router A.S.I.C Paper at I.S.S.R.D-I.C.S.C.D SANDIEGO, U.S.A., Accepted Journal at High Reputed Journal – Mitteilungen-Klosternburg Weiner Strasse, AUSTRIA, Europe etc.), and also J.M.E.S.T - Germany .

Dr. D.N Rao B. Tech, M.E, Ph.D, Dean R&D ,JBIET earlier he worked as a principal of JBREC,

Hyderabad. His carrier spans nearly three decades in the field of teaching, administration, R&D, and other diversified in-depth experience in academics and administration. He has actively involved in organizing various conferences and workshops. He has published over 11 international journal papers out of his research work. He presented more than 15 research papers at various national and international conferences. He is Currently approved reviewer of IASTED International journals and conferences from the year 2006. He is also guiding the projects of PG/Ph.D students of various universities

Dr.Vathsal Currently working as a Professor- Aero Dept. I.A.R.E, earlier He Was Dean R&D ,JBIET , He Obtained PhD from I.I.S.C,Bangalore,also Did Post Doctoral Research in DFVLR,Germany and NASA Goddard Space Flight Centre,USA,and also he worked with keen Designations Scientist E,F,G from Reputed Govt R&D Industry Organizations over past years and closely worked with Dr.A.P.J Abdul Kalam He Published lot of various national, international journals & conferences, He guiding 5 PhD Students from Various universities. He Got Prestigious awarded as a Noble Son of India.